## EFFICIENT RAY TRACING ARCHITECTURES

by

Josef Bo Spjut

A dissertation submitted to the faculty of

The University of Utah

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in

Computing

School of Computing

The University of Utah

May 2015

Copyright © Josef Bo Spjut 2015

All Rights Reserved

# The University of Utah Graduate School

## STATEMENT OF DISSERTATION APPROVAL

| The dissertation of                            | Josef Bo Spjut |                             |

|------------------------------------------------|----------------|-----------------------------|

| has been approved by the following supervisory |                |                             |

| Erik Brunvand                                  | , Chair        | Dec 20, 2013  Date Approved |

| Alan Davis                                     | , Member       | Dec 20, 2013  Date Approved |

| Rajeev Balasubramonian                         | , Member       | Dec 20, 2013 Date Approved  |

| Peter Shirley                                  | , Member       | Dec 20, 2013 Date Approved  |

| Ingo Wald                                      | , Member       | Sep 17, 2014 Date Approved  |

|                                                |                |                             |

| and by Alan Davis                              | 5              | _ , Chair/Dean of           |

| the Department/College/School of               | Computing      |                             |

| and by David B. Kieda, Dean of The Graduate S  | chool.         |                             |

## ABSTRACT

This dissertation presents computer architecture designs that are efficient for ray tracing based rendering algorithms. The primary observation is that ray tracing maps better to independent thread issue hardware designs than it does to dependent thread and data designs used in most commercial architectures. While the independent thread issue causes extra overhead in the fetch and issue parts of the pipeline, the number of computation resources required can be reduced through the sharing of less frequently used execution units. Furthermore, since all the threads run a single program on multiple data (SPMD), thread processors can share instruction and data caches. Ray tracing needs read-only access to the scene data during each frame, so caches can be optimized for reading, and traditional cache coherence protocols are unnecessary for maintaining coherent memory access. The resultant image exists as a write only frame buffer, allowing memory writes to avoid the cache entirely, preventing cache pollution and increasing the performance of smaller caches.

Commercial real-time rendering systems lean heavily on high-performance graphics processing units (GPU) that use the rasterization and z-buffer algorithms for rendering. A single pass of rasterization throws out much of the global scene information by streaming the surface data that a ray tracer keeps resident in memory. As a result, ray tracing is more naturally able to support rendering effects involving global information, such as shadows, reflections, refractions and camera lens effects. Rasterization has a time complexity of approximately O(Nlog(P)) where N is the number of primitive polygons and P is the number of pixels in the image. Ray tracing, in contrast, has a time complexity of O(Plog(N)) making ray tracing scale better to large scenes with many primitive polygons, allowing for increased surface detail. Finally, once the number of pixels reaches its limit, ray tracing should exceed the performance of rasterization by allowing the number of objects to increase with less of a penalty on performance.

# CONTENTS

| AE  | BSTRACT                                                                                                                                                                                                                                                                                        | iii                                                |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| LIS | ST OF FIGURES                                                                                                                                                                                                                                                                                  | vi                                                 |

| LIS | ST OF TABLES                                                                                                                                                                                                                                                                                   | ix                                                 |

| AC  | CKNOWLEDGMENTS                                                                                                                                                                                                                                                                                 | x                                                  |

| CH  | HAPTERS                                                                                                                                                                                                                                                                                        |                                                    |

| 1.  | INTRODUCTION                                                                                                                                                                                                                                                                                   | 1                                                  |

|     | <ul> <li>1.1 Existing Approaches to Graphics Processing</li> <li>1.2 Raster Graphics</li> <li>1.3 Ray Tracing</li> <li>1.3.1 Acceleration Structures</li> <li>1.3.2 Ray Tracing Optimizations</li> <li>1.4 Applications and Scenes</li> <li>1.5 Dissertation</li> </ul>                        | 1<br>4<br>5<br>7<br>8<br>10<br>11                  |

| 2.  | A MIMD THROUGHPUT COMPUTE SOLUTION                                                                                                                                                                                                                                                             | 15                                                 |

|     | 2.1 Parallelism Considerations 2.1.1 Nonparallel Applications 2.1.2 Parallel but Branchy 2.2 The TRaX Architecture 2.2.1 A Thread Processor 2.2.2 A Collection of Threads in a Thread Multiprocessor 2.2.3 Top Level Chip 2.2.4 Functional Units 2.3 Example TRaX Architectures 2.4 Conclusion | 16<br>17<br>18<br>18<br>21<br>23<br>24<br>25<br>26 |

| 3.  | TRAX SIMULATION                                                                                                                                                                                                                                                                                | 27                                                 |

|     | 3.1 Simulation Configuration 3.2 Simulation Parameters 3.3 Simulation Initialization 3.4 Execution 3.5 End of Simulation 3.6 Example Simulation                                                                                                                                                | 28<br>29<br>30<br>32<br>34<br>35                   |

| 4. | PROGRAMMING TRAX                                            | 38             |

|----|-------------------------------------------------------------|----------------|

|    | 4.1 TRaX Helper Functions4.2 Register Stack4.3 LLVM Backend | 40<br>40<br>40 |

|    | 4.4 Functional Simulation                                   | 42             |

|    | 4.5 Example TRaX Programs                                   | 42             |

|    | 4.6 Ray Tracing Software                                    | 45             |

|    | 4.6.1 Shading Methods                                       | 46             |

|    | 4.6.2 Procedural Texturing                                  | 46             |

|    | 4.6.3 Path Tracer Application                               | 47             |

| 5. | EVALUATION OF RAY TRACING ON TRAX                           | 50             |

|    | 5.1 Design of a Threaded Multiprocessor                     | 51             |

|    | 5.1.1 Multi-TM Chip                                         | 52             |

|    | 5.1.2 Whitted-Style Ray Tracer                              | 53             |

|    | 5.1.3 Design Exploration                                    | 54             |

|    | 5.1.4 Functional Units                                      | 55             |

|    | 5.1.5 Single TM Performance                                 | 56             |

|    | 5.1.6 Secondary Ray Performance                             | 60             |

|    | 5.2 Overall Chip Design                                     | 64             |

|    | 5.2.1 Architectural Exploration Procedure                   | 64             |

|    | 5.2.2 Thread Multiprocessor (TM) Design                     | 66             |

|    | 5.2.3 Exploring Constrained Resource Configurations         | 68             |

|    | 5.2.4 Results                                               | 74             |

|    | 5.3 Mobile Ray Tracing                                      | 76             |

|    | 5.3.1 Architecture and Methodology                          | 77             |

|    | 5.3.2 Results                                               | 79             |

|    | 5.3.3 Memory Bandwidth Concerns                             | 81             |

|    | 5.4 Conclusion                                              | 83             |

| 6. | RELATED WORK                                                | 85             |

|    | 6.1 High Performance GPU Architectures                      | 85             |

|    | 6.1.1 NVIDIA Fermi                                          | 87             |

|    | 6.1.2 NVIDIA Kepler                                         | 88             |

|    | 6.1.3 AMD Cypress and Cayman                                | 88             |

|    | 6.1.4 AMD Graphics Core Next (GCN)                          | 89             |

|    | 6.2 Low Power Commercial Architectures                      | 90             |

|    | 6.2.1 Tegra                                                 | 91             |

|    | 6.2.2 PowerVR                                               | 91             |

|    | 6.3 General Purpose Architectures                           | 91             |

|    | 6.3.1 SIMD Extensions to CPUs                               | 92             |

|    | 6.3.2 Cell Architecture                                     | 93             |

|    | 6.3.3 Larrabee, Intel MIC, and Xeon Phi                     | 93             |

|    | 6.4 High Performance Research Architectures                 | 94             |

|    | 6.4.1 StreamRay                                             | 94             |

|    | 6.4.2 Rigel                                                 | 94             |

|    | 6.4.3 RPU                                                   | 95             |

|               | 6.4.4 Copernicus                   | 95  |

|---------------|------------------------------------|-----|

|               | 6.5 Low-Power Ray Tracing Research | 96  |

|               | 6.5.1 ENCORE                       | 96  |

|               | 6.5.2 MRTP                         | 96  |

|               | 6.6 Conclusion                     | 97  |

| 7.            | CONCLUSIONS AND FUTURE WORK        | 98  |

|               | 7.1 TRaX-style Programs            | 99  |

|               | 7.1.1 SIMD Efficiency in TRaX      | 100 |

|               | 7.1.2 TRaX Rasterizer              |     |

|               | 7.2 Future Work                    | 102 |

| $\mathbf{RE}$ | FERENCES                           | 107 |

# LIST OF FIGURES

| 1.1 | The Z-buffer Algorithm                                                                                                                                                                                                                                         | 3  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | OpenGL Pipeline                                                                                                                                                                                                                                                | 4  |

| 1.3 | The Ray Tracing Algorithm                                                                                                                                                                                                                                      | 6  |

| 1.4 | Example Ray Traced Scenes                                                                                                                                                                                                                                      | 11 |

| 1.5 | Path Traced Images from Lux [1] at 128 Samples Per Pixel                                                                                                                                                                                                       | 14 |

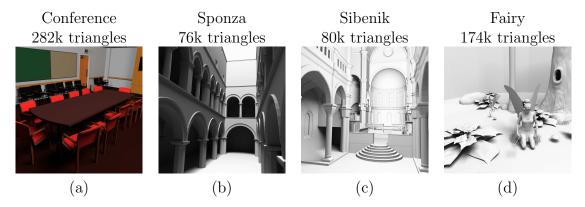

| 2.1 | Test Scenes Used to Evaluate Performance. (a) Conference (b) Sponza Atrium (c) Sibenik Cathedral (d) Fairy Forest                                                                                                                                              | 19 |

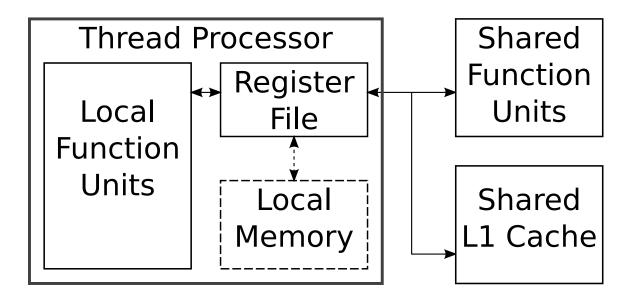

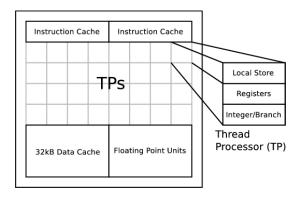

| 2.2 | Thread Processor Block Diagram                                                                                                                                                                                                                                 | 21 |

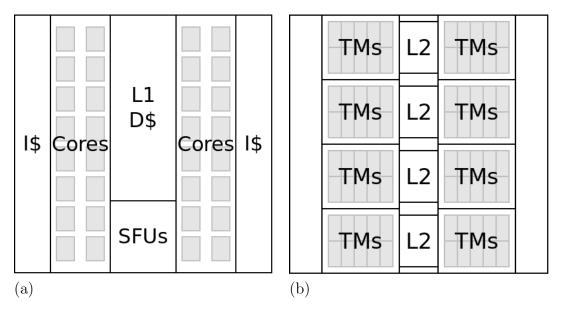

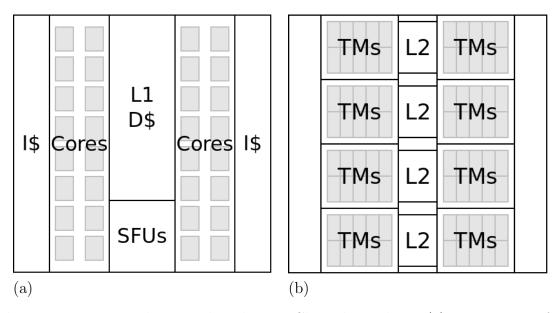

| 2.3 | Potential TM and Multi-TM Chip Floor Plans. (a) TM Layout of 32 TPs and Shared Resources. (b) Chip with Multiple TMs Sharing L2 Caches                                                                                                                         | 23 |

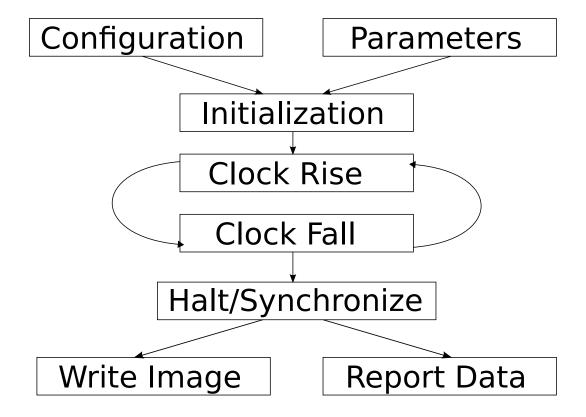

| 3.1 | Simulator Overview                                                                                                                                                                                                                                             | 29 |

| 3.2 | Example Hardware Configuration File                                                                                                                                                                                                                            | 30 |

| 3.3 | Example Functional Unit Utilization                                                                                                                                                                                                                            | 37 |

| 4.1 | Gradient Fill Example                                                                                                                                                                                                                                          | 43 |

| 4.2 | Path Tracer Example                                                                                                                                                                                                                                            | 44 |

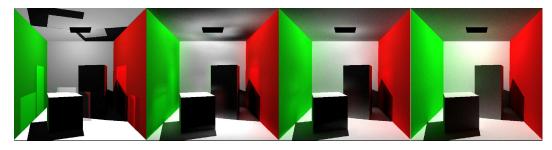

| 4.3 | The Cornell Box Scene Showing the Visual Change as the Sampling Angle Increases in our Path Tracer. Starting on the Left: 0 Degrees, 30 Degrees, 60 Degrees, and 180 Degrees on the Right                                                                      | 49 |

| 5.1 | Test Scenes Rendered on Our TRaX Architectural Simulator                                                                                                                                                                                                       | 53 |

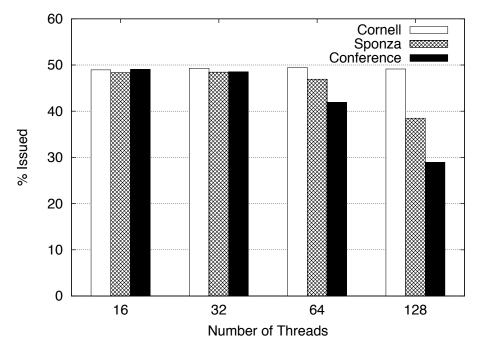

| 5.2 | Thread Performance (% Issued)                                                                                                                                                                                                                                  | 59 |

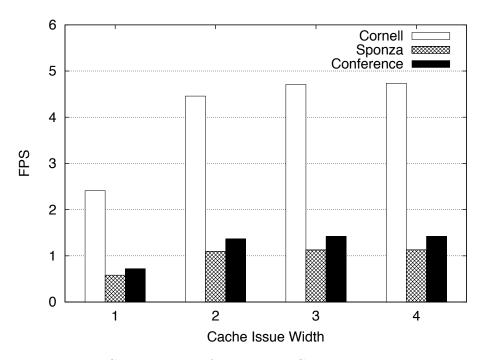

| 5.3 | Single TM Performance as Cache Issue Width is Varied                                                                                                                                                                                                           | 59 |

| 5.4 | Test Scenes Used to Evaluate Performance. (a) Conference (b) Sponza Atrium (c) Sibenik Cathedral (d) Fairy Forest                                                                                                                                              | 65 |

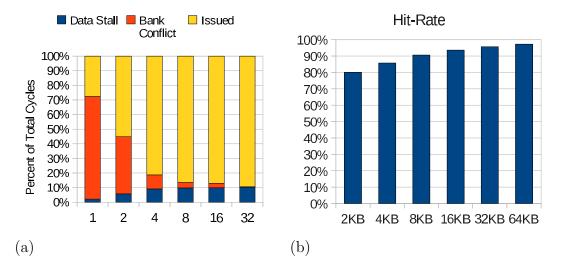

| 5.5 | L1 Data Cache Performance for a Single TM with Over-Provisioned Functional Units and Instruction Cache. (a) Issue Rate for Varying Banks in a 2KB Data Cache. (b) Dcache Hit%, 8-banks and Varying Capacities                                                  | 69 |

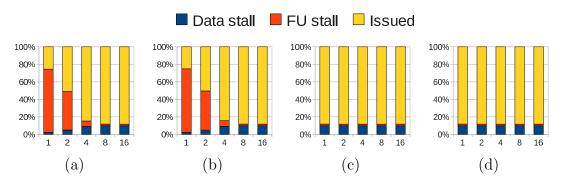

| 5.6 | Effect of Shared Functional Units on Issue Rate Shown as a Percentage of Total Cycles. (a) FP Add/Sub (13% of Issued Insts). (b) FP Multiply (13% of Issued Insts). (c) FP Inverse Square Root (0.4% of Issued Insts). (d) Int Multiply (0.3% of Issued Insts) | 70 |

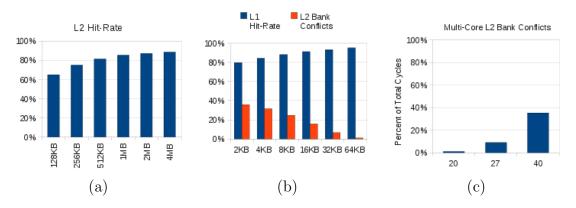

| 5.7  | L2 Performance for 16 Banks and TMs with the Top Configuration<br>Reported in Table 5.9. (a) Hit-rate for Varying L2 Capacities with 20<br>TMs Connected to Each L2. (b) Percentage of Cycles not Issued Due to<br>L2 Bank Conflicts for Varying L1 Capacities (and Thus Hitrates) for 20 |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | TMs. (c) L2 Bank Conflicts for a Varying Number of TMs Connected to Each L2. Each TM Has a 64KB L1 Cache with 95% Hitrate                                                                                                                                                                 | 72 |

| 5.8  | Potential TM and Multi-TM Chip Floor Plans. (a) TM Layout of 32 Threads and Shared Resources. (b) Chip with Multiple TMs Sharing L2 Caches                                                                                                                                                | 73 |

| 5.9  | A 32-thread TM with Shared Caches and FPUs                                                                                                                                                                                                                                                | 78 |

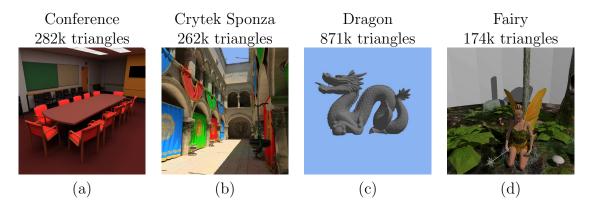

| 5.10 | Test Scenes Used to Evaluate Mobile Performance. (a) Conference (b) Crytek Sponza (c) Dragon (d) Fairy Forest                                                                                                                                                                             | 82 |

# LIST OF TABLES

| 3.1 | Simulation Parameters                                                                                                                                                                                                                                                                                                                                                                                                                  | 31 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Example Memory Layout                                                                                                                                                                                                                                                                                                                                                                                                                  | 33 |

| 3.3 | Example Simulation Configurations                                                                                                                                                                                                                                                                                                                                                                                                      | 36 |

| 4.1 | Helper Functions                                                                                                                                                                                                                                                                                                                                                                                                                       | 41 |

| 5.1 | Scene Data with Results for 1 and 16 TMs, Each with 32 Thread Processors, and Phong Shading Estimated at 500MHz                                                                                                                                                                                                                                                                                                                        | 54 |

| 5.2 | Default Functional Unit Mix (500MHz Cycles)                                                                                                                                                                                                                                                                                                                                                                                            | 55 |

| 5.3 | Area Estimates (Prelayout) for Functional Units Using Artisan CMOS Libraries and Synopsys. The 130nm Library is a High Performance Cell Library and the 65nm is a Low Power Cell Library. Speed is Similar in Both Libraries.                                                                                                                                                                                                          | 55 |

| 5.4 | TRaX Area Estimates to Achieve 30 FPS on Conference. These Estimates Include Multiple TMs, but not the Chip-Wide L2 Cache, Memory Management, or Other Chip-Wide Units                                                                                                                                                                                                                                                                 | 58 |

| 5.5 | Performance Comparison for Conference and Sponza Assuming a Fixed Chip Area of $150mm^2$ , not Including the L2 Cache, Memory Management, and Other Chip-Wide Units.                                                                                                                                                                                                                                                                   | 58 |

| 5.6 | Performance Comparison for Conference Against Cell and RPU. Comparison in Frames Per Second and Million Rays Per Second (MRPS). All Numbers Are for Shading with Shadows. TRaX and RPU Numbers are for 1024×768 Images. Cell Numbers are for 1024×1024 Images. The Cell is Best Compared Using the MRPS Metric Which Factors Out Image Size                                                                                            | 61 |

| 5.7 | Results are Reported for the Conference and Sponza Scenes at Two Different Resolutions with a Different Number of Rays Per Pixel. Path Traced Images Use a Fixed Ray Depth of Three. TRaX Results Are for a Single TM with 32 Thread Processors Running at a Simulated 500 MHz. Manta Numbers are Measured Running on a Single TM of an Intel Core2 Duo at 2.0GHz. Speed Results are Normalized to Path Tracing with a 10 Degree Cone. | 63 |

| 5.8 | Functional Unit Areas and Performance                                                                                                                                                                                                                                                                                                                                                                                                  | 67 |

| 5 9 | Optimal TM Configurations in Terms of MRPS/mm <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                             | 70 |

| 5.10 | GTX285 SM vs. MIMD TM Resource Comparison. Area Estimates Are Normalized to Our Estimated FU Sizes from Table 5.8, and Not From Actual GTX285 Measurements.                                                                                                               | 71  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.11 | A Selection of Our Top Chip Configurations and Performance Compared to an NVIDIA GTX285 and Copernicus.                                                                                                                                                                   | 73  |

| 5.12 | Comparing Our Performance on Two Different Configurations to the GTX285 for Three Benchmark Scenes [2]. Primary Ray Tests Consisted of 1 Primary and 1 Shadow Ray Per Pixel. Diffuse Ray Tests Consisted of 1 Primary and 32 Secondary Global Illumination Rays Per Pixel | 75  |

| 5.13 | Comparison of Mobile Graphics Accelerator Architectures. All Accelerators Are Scaled to 65nm and 500 MHz Naively for Better Comparison with Our Configurations. *Tegra 2 Die Size is Estimated from a Die Photo                                                           | 80  |

| 5.14 | Ray Tracing Performance, Shown in Millions of Rays Per Second                                                                                                                                                                                                             | 82  |

| 5.15 | Performance in Millions of Rays Per Second with the Baseline and Increased Memory Bandwidth for the Dragon Scene as Well as an Average Across All Scenes Tested                                                                                                           | 83  |

| 7.1  | SIMD Performance: Conference Scene                                                                                                                                                                                                                                        | 102 |

### ACKNOWLEDGMENTS

I took a long path to get to this point where I was able to complete this dissertation. Obviously, I did not become who am I or complete all of this work on my own, so I would like to take this chance to acknowledge some of the influences on my life up to this point.

First, I feel a need to recognize my dad, Erik Spjut, for instilling in me a curiosity about this world from my youth. When I found a book on programming in elementary school, he installed a compiler and encouraged me to start programming. He also was a big part of the reason I ended up at the University of Utah, it being his undergraduate alma mater. From my childhood, I always had a desire to pursue a Ph.D. since the man I looked up to most had one.

I also would be negligent to not mention my mother, Karen Spjut, who has done her best to encourage and support me through all the years. I remember the many times in my primary and secondary education where she would stay up late or rise extremely early to provide moral support while I completed my school work. Unfortunately, I have not yet been able to break this trend, as anyone who worked on a paper deadline with me can attest to.

When it came time to select a graduate school and advisor, I really did not know what I was looking for or what would be important for me in completing graduate school. I managed to secure a position working with Erik Brunvand working on a project I was and am passionate about (much of which is represented in this dissertation). Erik was a great example for me and was the perfect advisor for keeping my mental stability even though I was not always able to complete all tasks as promptly as we would have liked. Erik helped me develop as a researcher, but he also encouraged artistic expression, and helped me develop my teaching ability as much as I let him.

I should also thank my committee, Al Davis, Rajeev Balasubramonian, Pete Shirley, and Ingo Wald for the encouragement, support, and many great discussions we had over the years. I was able to work with a number of excellent graduate students as well, but feel an extra acknowledgement should be given to Daniel Kopta, who was a co-author for all of the papers that contributed to this dissertation. The Utah architecture lab members gave me valuable feedback and provided many enjoyable conversations and diversions over the years. I should also thank Karen Feinauer and Ann Carlstrom for the excellent institutional support they provided.

### CHAPTER 1

## INTRODUCTION

Computer generated images are used for many professional tasks including movies, video games, computer aided drafting, visualization, medical imaging, and others. These images are useful for reducing costs, providing added insight, and increasing the effectiveness of workers in their respective fields. There are two principal metrics that the users of these applications want from image rendering: image quality and speed of image synthesis, often called framerate. In situations where image quality is the most important, offline rendering is typically used where a computer, or a cluster of computers, spends a very long time to generate one image. When framerate and interactivity are more important, shortcuts are taken and often special purpose hardware is used to generate images many times a second. A common metric to measure speed of rendering is the number of frames per second which is usually abbreviated as fps. In both cases, there are two primary classes of algorithms used: rasterization and ray tracing. While other methods for image synthesis do exist, this dissertation will focus primarily on these two techniques. Considering a first order approximation, rasterization algorithms scale linearly with the number of triangles or primitives in the scene while ray tracing algorithms scale linearly with the number of pixels or samples in the final image. Both algorithms have been used in both offline rendering (seconds to hours per frame), and interactive (5-15 fps) to real-time (20+ fps) rendering.

## 1.1 Existing Approaches to Graphics Processing

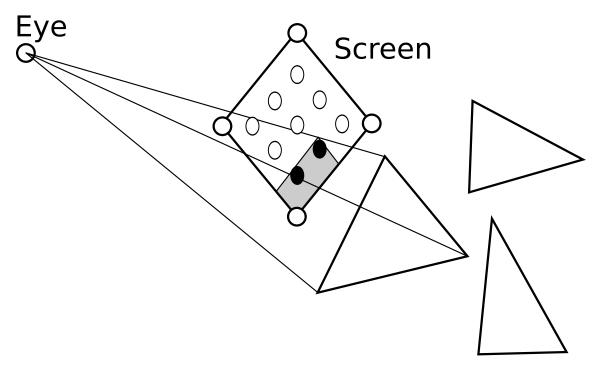

At present almost every personal computer has a dedicated processor that enables interactive 3D graphics, whether a discrete add-in card or integrated on the same die as the main CPU. These graphics processing units (GPUs) implement some version of the *z-buffer* algorithm introduced in Catmull's landmark University of

Utah dissertation [3]. In this algorithm the inner loop iterates over all triangles in the scene and projects those triangles to the screen. It computes the distance to the screen (the z-value) at each pixel covered by the projected triangle and stores that distance in the z-buffer. Each pixel is updated to the color of the triangle (perhaps through an image-based texture lookup or through a procedural texturing technique) unless a smaller distance, and thus a triangle nearer to the screen, has already been written to the z-buffer (see Figure 1.1). A huge benefit of this approach is that all triangles can be processed independently with no knowledge of other objects in the scene. Current mainstream commercial graphics processors use highly efficient z-buffer rasterization hardware to achieve impressive performance in terms of triangles processed per second. This hardware generally consists of deep nonbranching pipelines of vector floating point operations as the triangles are streamed through the GPU and specialized memory systems to support texture lookups. However, the basic principle of z-buffer rasterization, that triangles are independent, becomes a bottleneck for highly realistic images. This assumption limits shading operations to per-triangle or per-pixel computations and does not allow for directly computing global effects such as shadows, transparency, reflections, refractions, or indirect illumination. Tricks are known to approximate each of these effects individually, but combining them is a daunting problem for the z-buffer algorithm. The most common trick is to add an extra pass through all of the geometry in the scene, but that is inherently wasteful since it consumes communication resources for redundant data.

Modern GPUs can interactively display several million triangles in complex 3D environments with image-based (look-up) texture and lighting. The wide availability of GPUs has revolutionized how work is done in many disciplines, and has been a boon to the hugely successful video game industry. While the hardware implementation of the z-buffer algorithm has allowed excellent interactivity at a low cost, there are (at least) three classes of applications that have not benefited significantly from this revolution:

• those that have datasets much larger than a few million triangles such as vehicle design, landscape design, manufacturing, complex movie scenes, and some branches of scientific visualization:

Figure 1.1: The Z-buffer Algorithm

- those that have nonpolygonal data not easily converted into triangles;

- those that demand high quality shadows, reflection, refraction, and indirect illumination effects such as architectural lighting design, rendering of outdoor scenes, realistic movie scenes, and vehicle lighting design.

These classes of applications typically use Whitted's ray tracing algorithm [4, 5, 6]. The ray tracing algorithm is better suited to huge datasets than the z-buffer algorithm because its natural use of hierarchical scene structuring techniques allows image rendering time that is sublinear in the number of objects. While z-buffers can use some hierarchical culling techniques, the basic algorithm is linear with respect to the number of objects in the scene. It is ray tracing's larger time constant and lack of a commodity hardware implementation that makes the z-buffer a faster choice for datasets that are not huge. Ray tracing is better suited for creating shadows, reflections, refractions, and indirect illumination effects because it can directly simulate the physics of light based on the light transport equation [7, 8]. By directly and accurately computing composite global visual effects using ray optics, ray tracing can create graphics that are problematic for the z-buffer algorithm. Ray tracing

also provides flexibility in the intersection computation for the primitive objects, which allows nonpolygonal primitives such as splines or curves to be represented directly. Unfortunately, computing these visual effects based on simulating light rays is computationally expensive.

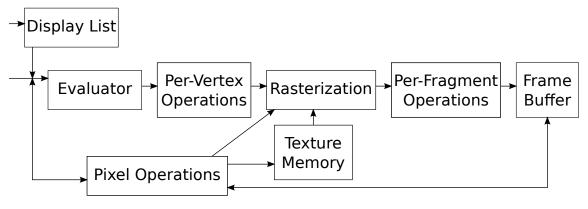

## 1.2 Raster Graphics

Commercial hardware for rasterization must all implement an interface to the widely used OpenGL [9] and DirectX [10] libraries in order to be competitive. Both libraries are very similar and perform the same set of functions, but with subtle differences. To understand how graphics hardware is implemented, it is interesting to examine the OpenGL pipeline (chosen because it is an open standard). The OpenGL Programming Guide [11] discusses the key stages in the OpenGL pipeline, which include: pixel operations, per-vertex operations, texture assembly, rasterization, and per-fragment operations, as seen in Figure 1.2. In older GPU architectures, the programmable vertex and pixel shaders were handled by separate pipeline units, but modern GPUs have become unified and perform all programmable processing in the same set of units. Advanced Micro Devices (AMD) recently announced Mantle [12] technology uses the same style of processing while exposing different parts of the underlying architecture explicitly to the programmer.

Rasterization is known to work well in single instruction multiple data (SIMD) execution, which is why GPUs that are optimized for it are SIMD architectures. Each triangle is first projected to screen space, a series of operations that are repeated

Figure 1.2: OpenGL Pipeline

for each triangle, as can be seen in Figure 1.1. This projection is performed by multiplying each vertex by a 4x4 transformation matrix to place it in the *canonical viewing volume*. Each vertex can also have operations performed on it which are repeated for each vertex, and are optimally nondivergent. Subsequently, a set of fragments are generated by an optimized scan-line conversion process, which when using the same bounding box, does not diverge. Then shading is performed on each of the fragments that graduates into the frame buffer by passing a "z" test. Each phase of typical rasterization can easily be mapped to efficient SIMD execution. Due to the fact that triangles are considered to be entirely independent, rasterization lends itself well to GPU-style SIMD.

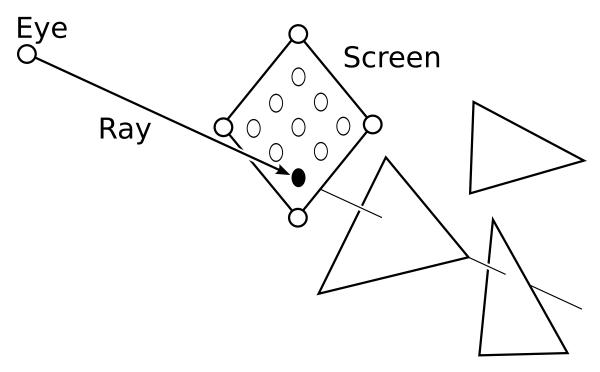

## 1.3 Ray Tracing

Ray tracing as an algorithm is designed to approximate the physics of light and more easily achieves some of the complex lighting effects that are more difficult to achieve with rasterization. Much work is being done to attempt to bring the ray tracing algorithm to real time, or at least interactive frame rates. Most modern ray tracers resemble to a great extent the 1980s Whitted ray tracer [4] with improvements and optimizations.

While the ray tracing algorithm is not particularly parallel at the instruction level, it is extremely (embarrassingly) parallel at the thread level. Ray tracing's inner loop considers each pixel on the screen. At each pixel a 3d half-line (a "ray") is sent into the set of objects and returns information about the closest object hit by that ray. The pixel is colored (again, perhaps using texture lookups or a procedurally computed texture) according to this object's properties (Figure 1.3). This line query, also known as "ray casting" can be repeated recursively to determine shadows, reflections, refractions, and other optical effects. In the extreme, every ray cast in the algorithm can be computed independently. What is required is that every ray have read-only access to the scene database, and write-only access to a pixel in the frame buffer. Importantly, threads never have to communicate with other threads (except to partition work among the threads, which is done using an atomic increment instruction in our implementation). This type of memory utilization means that a

Figure 1.3: The Ray Tracing Algorithm

relatively simple memory system can keep the multiple threads supplied with data. It should be noted that some level of parallelism can be extracted by intersecting a given ray with multiple triangles at once, something that is exploited by Intel's Embree [13, 14].

The three main kernels of a ray tracer are traversal, intersection, and shading. Traversal is the first phase of ray tracing computation and involves the traversal of a tree-like structure to reduce the number of intersection tests that must be performed. These tree-like structures are called acceleration structures and are discussed in more detail in Section 1.3.1. Intersection is the phase of ray tracing where rays are tested for intersection with the primitive objects in the scene being rendered. Shading is the final stage of computation where the final color is determined based on the color of objects, the positions of the lights and the impact of other objects in the scene on the illumination of objects. Shading in ray tracing is essentially identical to shading in rasterization with an important difference being the casting of additional rays for secondary lighting effects. Most of the general improvements that have been made for shading on GPU-based rasterizers can be applied to shading when using a ray

tracer. Therefore the two most interesting phases to look at when improving ray tracing performance are the traversal and intersection.

Primitive intersection involves computing the intersection of a ray with a primitive, usually a triangle. A system which includes programmable intersection operations could easily be extended to intersect arbitrary types of geometric primitives, however, triangles are the most interesting for supporting legacy scenes and current production tools for video games and movies (to a lesser extent). From each point where the ray intersects an object in the scene, an additional "secondary" ray can be recursively cast into the scene to determine optical effects such as shadows, reflections, refraction, caustics (focused light from an indirect source), and other global illumination and optical effects. Ray tracing has distinct advantages over rasterization in terms of its ability to easily render these optical effects, making ray tracing the rendering algorithm of choice for highly realistic images. Ray tracing can also be effectively used for traversing volumetric data and large datasets, such as medical images and other scientific data. Work has been done to optimize the exact computation done when intersecting a ray with a triangle [15, 16], but without a smart method to choose which rays need to check for intersection with which triangles, an exhaustive search of the triangles would need to be performed.

#### 1.3.1 Acceleration Structures

An acceleration structure is used by a ray tracer to greatly improve the speed and efficiency of rendering. Without an acceleration structure, the total render time for a scene is on the order of the number of pixels times the number of objects in the scene. It is the acceleration structure that allows for logarithmic time complexity in the number of objects in the scene. In order for an acceleration structure to work most efficiently, it would instantly determine which objects in the scene are intersected by the ray in question, and which ones are missed entirely. A simple example would be the case where the entire set of objects in the scene can be enclosed by a single box, and by performing a single ray-box intersection test, the ray tracer can find if a ray misses the box entirely, therefore missing the scene entirely. This single intersection test is much quicker than performing an intersection test with all but the most trivial

scenes. When the ray-box test comes back positive, then the ray tracer does not know whether an object is actually hit or not, and additional computation must be performed. The scene could then be further divided into subscenes, each with their own bounding box, in order to hopefully eliminate large chunks of the geometry from each intersection test. While this technique is useful, the performance of an acceleration structure varies greatly from scene to scene and can also depend on the ray direction and which kind of build technique was used to generate the acceleration structure.

A variety of acceleration structures are used regularly in ray tracers [17] including KD-trees, bounding volume hierarchies (BVH), and grids. While each acceleration structure has its benefits, this work uses BVHs because they guarantee that each triangle is in only one leaf node and that each leaf node has at least one triangle in it and are fairly efficient at removing unnecessary volumes of space quickly. The performance of traversing an acceleration structure can be improved by either optimizing the creation of the structure for better run-time performance [18], or by using a structure that better culls away the empty space. BVHs are typically used for most animations because a simple refit can be performed relatively cheaply without a huge loss in traversal performance over time [19, 20]. Some work is more focused on reducing the build time of structures to facilitate dynamic scenes [21].

### 1.3.2 Ray Tracing Optimizations

Since recent GPU and CPU architectures depend heavily on SIMD for performance, work has been done to parallelize ray traversal across 4-wide (or sometimes wider) SIMD units. Typically a set of rays are grouped together in a packet to be traced together. This packet is further simplified during traversal by using a proxy for the packet, such as a frustum [22, 23] or a subset of the rays in the packet [24]. These techniques, often called *packet tracing*, are known to work well for primary visibility in ray tracing, but are less efficient when the rays become less spatially coherent, which happens when generating the more interesting lighting effects that are desired from ray tracing. Parallelization has also been analyzed for the construction of acceleration structures [25].

NVIDIA introduced their OptiX engine for ray tracing [26] to also take advantage of SIMD compute resources to accelerate ray tracing. They divide the ray tracing algorithm up into a set of kernels that can each execute independently (though they might just be different inner loops of what is called a "megakernel") to reduce the impact of divergence in the acceleration structure traversal. This technique requires additional overhead in managing the individual threads and efficiently assigning the threads to available execution resources. In the Fermi architecture [27] and beyond, much effort has been put forth to allow for multiple simultaneous kernels to execute and for faster thread context switching. Wavefront formulation [28] has been proposed as an improvement over the more traditional megakernel approach. Other ray tracers have been made to use CPU SIMD extensions [14] and to even execute on architectures like the Cell [29]. These efforts require significant reorganization of memory and are no small task for the programmer to implement correctly.

A path tracer is similar in most ways to a ray tracer, especially in the overall flow of the program, however, the memory access pattern is different due to the selection of rays being traced. While the term "ray tracer" can describe a broad set of approaches involving the tracing of rays through a scene, a Cook-style path tracer [30] only traces a single path of light by randomly choosing one of the possible rays that could be chosen at each decision point. For example, when a ray hits a diffuse surface where the light is expected to bounce in any direction with equal probability, the secondary ray direction is chosen randomly in the hemisphere described by the normal at that intersection point. Similarly, when approximating blurry reflections, the ray directions will prefer to be chosen in some cone mostly facing the direction of a perfect reflection on that surface. Due to the stochastic sampling performed by Cook-style path tracers, a large number of samples should be gathered per pixel in order for the final image to converge to a set of values that are close to correct.

Some applications are not currently close to being interactive on GPUs regardless of image quality because their number of primitive objects N is very large. These include many scientific simulations [31], the display of scanned data [32], and terrain rendering [33]. While level-of-detail (LOD) techniques can sometimes make display of geometrically simplified data possible, such procedures typically require costly prepro-

cessing and can create visual errors [34]. Simulation and games demand interactivity and currently use z-buffer/rasterization hardware almost exclusively. However, they spend a great deal of computational effort and programmer time creating complicated procedures for simulating lighting effects and reducing N by model simplification. In the end they have images of inferior quality to those generated by ray tracing. I believe that these industries based on interactive graphics rendering would use ray tracing if a solution existed that were fast enough.

As mentioned previously, shading is an important part of both ray tracing and rasterization. The computations involved are the same and the architectural and algorithmic improvements for GPU rasterizers as well as offline renderers are applicable to both algorithms. A variety of shading techniques are commonly used, such as Gouraud [35] and Phong [36] shading. Image textures or computed textures can be sampled as well to get the base color for the shading computation and can also be used to perform bump mapping [37].

## 1.4 Applications and Scenes

In this dissertation, there are two kinds of ray tracers used to evaluate the architectural improvements. They are discussed in more detail in Section 4.6. The first ray tracer is a Kajiya style [8] ray tracer that supports recursive ray tracing and standard surface shading techniques (lambertian and phong). This Kajiya ray tracer only supports a single light source, and casts a shadow ray during shading to determine if the surface is in light or shadow. A version of this type of ray tracer exists written entirely in our TRaX assembly language, another compiled for a variable number of registers with the call stack in registers, and a third compiled for 32 registers using only the local store memory for program stack. The second kind of ray tracer is a Cook-style path tracer. The path tracer computes global illumination in the scene by allowing many samples to be taken while tracing each sample to a fixed ray depth on each run. The shading technique used is a Monte-Carlo sample lambertian shading. Some more advanced and varied rendering techniques have also been implemented successfully on the architecture, but they will not be represented in the results of this dissertation.

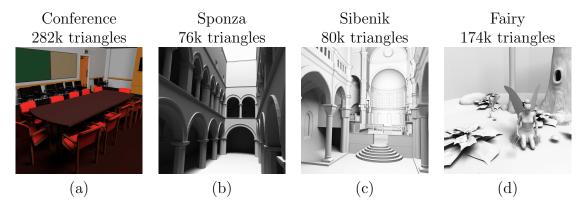

A number of different scenes are regularly used to evaluate the performance of ray tracers in order to allow for comparison of different techniques and modifications. Figure 1.4 shows a number of scenes that are used in a number of chapters in this dissertation. More details on these scenes and their use in simulation can be found in Chapter 5. In general, the scenes with higher triangle counts tend to require more memory bandwidth to render since they cannot fit in the caches and trend towards a larger working set. The scenes with fewer triangles tend to have fewer misses in the caches, and result in faster render times. However, the quality and kind of acceleration structure have a large affect on the render time of the scenes, so there are some experiments where a scene with relatively few triangles causes difficulty for the acceleration structure builder, resulting in more memory bandwidth usage, lower hit rates, and longer render times.

## 1.5 Dissertation

Most interactive graphics applications follow a trend of models increasing in size (Greenberg has argued that typical model sizes are doubling annually [38]). Most applications also demand increasingly more visual realism in order to provide more utility to their professional users and more enjoyment for video gamers. I believe these trends favor ray tracing in the future (either alone or in combination with rasterization for some portions of the rendering process). Following the example of graphics processing units (GPUs), I also believe that a special purpose architecture can be made capable of interactive ray tracing for large geometric models. Such special purpose hardware has the potential to make interactive ray tracing ubiquitous. Ray

Figure 1.4: Example Ray Traced Scenes

tracing can, of course, be implemented on general purpose CPUs, and on specially programmed GPUs. Both approaches have been studied, along with a few previous studies of custom architectures and more on these studies can be found in Chapter 6.

Both rasterization and ray tracing can be expressed as SPMD (single program multiple data) applications, where a single program is executed on each independent thread. This dissertation focuses on the ray tracing algorithm as the method of producing high quality images for future applications. While many ray tracers exist that run on CPUs, the architecture of a CPU has many features for general purpose processing that are not needed for ray tracing. GPUs use rasterization for rendering and are designed to accelerate rasterization even at the expense of general purpose computation performance. The fact that GPUs use SIMD (single instruction, multiple data) to perform rasterization suggests that rasterization maps well to a SIMD architecture. Note that while GPU vendors have frequently used the term SIMT (single instruction, multiple threads) to describe the fact that each data element in effect comes from a separate logical thread with hardware support for thread divergence, this dissertation generally uses the terms, SIMD, SIMT and GPU SIMD interchangeably, except where specified. Even though recent research has shown ways to map ray tracing to SIMD architectures, the ray tracing algorithm is generally not efficiently executed on SIMD hardware because of poor SIMD utilization. This lack of compatibility with SIMD hardware stems from the way any arbitrary group of rays is likely to intersect different objects in the scene. Rasterization hardware takes advantage of the independence of the triangles to stream them through wide SIMD computation units. Ray tracing, in contrast, performs a logarithmic-time lookup of the primitives, which can perform better when each independent lookup is allowed to become out of sync with other searches. This is more naturally supported in a loosely coupled SPMD/MIMD architecture, though there is extra overhead from a naive MIMD implementation. CPU SIMD extensions have been shown to increase performance greatly for CPU architectures, primarily because the SIMD extensions are included at a small overhead to the already large CPU architecture. It is possible to use simpler individual processing units for higher thread-level parallelism, removing the need for CPU SIMD extensions. The incremental overhead of adding extra

processing units can be greatly reduced by increasing the level of sharing among a group of these units where independent execution units provide little benefit.

In general, this dissertation explores architectural approaches to improving ray tracing performance, while still retaining a high level of programmability. Specifically, I will show that a throughput-oriented architecture with many simple cores operating in SPMD/MIMD mode can have significantly better performance on applications like ray tracing than fewer heavy-weight cores, like a CPU with SIMD extensions or an architecture where the threads are more closely coupled such as in a SIMD GPU. I present an architecture called TRaX (for Threaded Ray eXecution), which is specifically designed to exploit the opportunities available in the ray tracing algorithm for independent thread parallelism. This kind of parallelism is different from the SIMD style of parallelism that is so popular in current GPUs and CPUs, but is much better suited to ray tracing and other similarly branchy applications, though I provide no explicit analysis of other applications. In fact, CPUs and GPUs both support the same kind of parallelism as TRaX, but to a much lesser extent. Each core of a CPU is independent in the same way that each thread in TRaX is independent, and each SIMD cluster in a GPU could be caused to operate in a scalar fashion to also have independent thread execution. Clearly these techniques would greatly under-utilize the hardware available in both a CPU and a GPU, but are in fact what happens when those machines encounter the worst case program divergence. Using improvements proposed for the TRaX architecture, real time rendering can much more quickly approach the quality of the offline-rendered images seen in Figure 1.5. The existence of commercial ray tracing processors would cause a new revolution in the real-time rendering community.

$\textbf{Figure 1.5} : \ \, \text{Path Traced Images from Lux [1] at 128 Samples Per Pixel}$

## CHAPTER 2

# A MIMD THROUGHPUT COMPUTE SOLUTION<sup>123</sup>

As the title of this chapter suggests, the solution I propose for ray tracing involves MIMD (multiple instruction, multiple data) processing. TRaX (for threaded ray execution) is specifically designed to accelerate single-ray performance and to exploit thread-level parallelism using multiple thread processors and cores. Ray tracing is an application with the potential for massive amounts of thread-level parallelism. For example, a single frame of a 1080p HD image contains about two million pixels, each of which represents at least one primary ray. Furthermore, high quality ray tracing greatly benefits from increased sampling beyond a single primary ray (16 samples per pixel is a good start), and secondary rays can also be traced independently to create greater opportunities for thread-level parallelism. A high quality two million pixel ray traced image with two diffuse bounces and two point light sources along with 16 samples per pixel would involve 96 million illumination rays that require full shading computations and 192 million shadow rays that contribute to lighting through the same acceleration structure traversal for a total of 288 million rays. The potential number of parallel hardware threads that may improve the performance of a ray tracer is in the millions.

<sup>&</sup>lt;sup>1</sup>This chapter is modified with permission from J. Spjut, A. Kensler, D. Kopta, and E. Brunvand, "TRaX: A multicore hardware architecture for real-time ray tracing," *IEEE Transactions on Computer-Aided Design*, vol. 28, no. 12, pp. 1802 − 1815, Copyright ©2009 IEEE.

<sup>&</sup>lt;sup>2</sup>This chapter is modified with permission from D. Kopta, J. Spjut, E. Brunvand, and A. Davis, "Efficient MIMD architectures for high-performance ray tracing," in *IEEE International Conference on Computer Design (ICCD)*, Copyright ©2010 IEEE.

<sup>&</sup>lt;sup>3</sup>This chapter is modified with permission from J. Spjut, D. Kopta, E. Brunvand, and A. Davis, "A mobile accelerator architecture for ray tracing," in 3rd Workshop on SoCs, Heterogeneous Architectures and Workloads (SHAW-3), Copyright ©2012.

### 2.1 Parallelism Considerations

MIMD is a style of parallelism that involves duplicating the processor to allow multiple processors to execute in parallel. While it may initially appear trivial to duplicate a processor, there are a number of difficulties in allowing multiple processors to execute simultaneously, and nearly all of the difficulties involve the system required to deliver the data values to each processor. SIMD (Single Instruction, Multiple Data) instead exploits the situation when a program needs to perform the same basic operation on multiple pieces of data in parallel. If a single executing thread performs SIMD instructions, the processor is sometimes referred to as a vector processor since the multiple data elements can be thought of as a vector. When the multiple data elements are instead considered to come from independent threads, the term SIMT (Single Instruction, Multiple Threads) is often used. Typically, SIMT also indicates that the processor has hardware support for masking off computations for threads that may have divergent execution paths due to conditional branching.

A ray tracer can be expressed in a Single Program, Multiple Data (SPMD) programming model relatively easily. This single program could be executed using a traditional, single thread of execution trivially by allowing the program to loop over all tasks until they are all completed. A natural option would be to parallelize tasks using a MIMD processor with many hardware threads with full support for thread divergence. However, most commercial architectures include support for SIMD or SIMT processing, and as a result, heroic efforts are exerted to keep the data elements, or coupled threads from diverging as much as possible to match the underlying processor's limitations. I propose only using hardware features that work well with the natural behavior of the algorithm, rather than warping the fundamental ray tracing algorithm to match hardware designed for other applications.

Chapter 6 details many other architectures used for ray tracing [39, 40, 29, 41, 42, 43, 44, 45], which exploit parallelism using SIMD to execute some number of the same instructions at the same time. This technique does not scale well if the rays in the SIMD bundle become less coherent with respect to the scene objects they intersect [46]. In that case, what was a single SIMD instruction will have to be repeated for each of the threads as they branch to different portions of the scene and

require different intersection tests and shading operations. Because TRaX threads are independent we do not have to wastefully mask off results of functional unit operations.

SIMD works well as long as all of the threads attempt to execute the same instruction all the time. In fact, SIMD is better in this case because there is a reduction in the instruction fetch and decode stage of the pipeline. There exists a set of applications, however, that are known to not execute well on SIMD architectures because of poor utilization of the execution units. These applications suffer from many branches where a SIMD block has a high chance of diverging, causing some of the threads to execute different instructions than the rest of the threads.

There are some ways to reduce the loss in performance from divergent branching, such as filtering threads, and causing threads to block at certain points until the divergent threads reconverge. However, these techniques still result in additional overhead and reduced SIMD utilization. A standard high-performance ray tracer uses a tree-like acceleration structure to increase the performance of the visibility query per ray. Divergence comes when the individual rays take a different path through the data structure and end up in different phases of the computation. For instance, one thread may only need to intersect 32 nodes while another thread may require 1024 node intersection tests before moving on to triangle intersections. It is highly inefficient to have the first thread stand idle for such a large amount of time when it could continue on and begin working on a new ray. In fact, the percentage of threads able to issue on average per cycle is often used to report the efficiency of such SIMD systems and is called SIMD efficiency.

## 2.1.1 Nonparallel Applications

There exist some applications that are entirely serial in nature, or have a large percentage of the execution that cannot be made parallel. These applications are not very interesting in a study of parallel architectures since they do not benefit from any of the parallel improvements. CPUs are designed to extract instruction-level parallelism and can therefore do a good job of speeding up these applications without the use of SIMD extensions. Features like out-of-order issue, super-scalar use of multiple issue slots, and deep pipelines with aggressive branch prediction can improve

performance where SIMD and MIMD multithreading designs have essentially no effect on nonparallel program run-time.

## 2.1.2 Parallel but Branchy

There is another set of applications that are highly parallel, often called embarrassingly parallel, that can benefit greatly from a large number of parallel threads. In

many cases these applications have some outer loop that has few dependencies across

iterations of the loop, or at least dependencies that still allow for parallelization.

These applications are of the set that can benefit from parallel hardware implementations. SIMD is a good match for such an application as long as the time spent in one

iteration, and the instructions issued within that iteration, are relatively consistent.

When the core operations have a high amount of variability then a MIMD design is

likely to come out on top.

MIMD is a style of execution that, in contrast to SIMD, allows each parallel thread of execution to both operate on different data and execute different instructions. This can be found in multicore CPUs as each core executes its own instruction and is not required to execute the same instruction as any other core. Even on wide SIMD architectures like GPUs, there are many separate SIMD blocks that can each execute different instructions even though all the threads within a SIMD block must have the same instruction.

Vector computing is implemented very similarly to SIMD and the two terms are often used interchangeably in the literature. There is, however, a subtle difference between them and how these terms will be used here. Vector computing is when a single thread of execution has an operation to perform on data that can be thought of as a vector data type. So while SIMD executes many scalar operations from different threads or data streams in parallel, vector computing issues a vector operation from a single thread.

### 2.2 The TRaX Architecture

The vast majority of related commercial and research projects used to accelerate ray tracing depend on SIMD architectures to perform ray tracing. The huge constraint all of those projects deal with is the need for the threads executing in SIMD to remain synchronized as much as possible to achieve high SIMD utilization. Any time a thread in a SIMD block decides it needs to test for intersection of a node or primitive that the other threads do not need to test, the work is wastefully repeated for all of the other threads.

The TRaX architecture [47, 48, 49, 50, 51, 52] is a many-threaded architecture designed for fast ray tracing throughput. The approach is to optimize single-ray MIMD performance across many simple cores. This single-ray programming model loses some primary ray performance. However, it makes up for this by handling secondary rays (discussed in Section 1.3) nearly as efficiently as primary rays, where SIMD optimized ray tracers struggle. In addition to providing high performance, this approach can also ease application development by reducing the need to orchestrate coherent ray bundles. For the analysis of architectural options, a number standard ray tracing benchmark scenes are used, four of which are shown in Figure 2.1. More of the test scenes can be found in Chapter 5 along with detailed results from simulations. These scenes provide a representative range of performance characteristics.

Threads represent the smallest division of work in the ray-traced scene, so the performance of the entire system depends on the ability of the architecture to flexibly and efficiently allocate functional resources to the executing threads. As such, our architecture consists of a set of thread processors, called TPs, that include some functional units in each TP with other larger functional units being shared among nearby TPs. A collection of these TPs, their shared functional units, issue logic, and shared L1 cache are collected into a "thread multiprocessor," or TM.

**Figure 2.1**: Test Scenes Used to Evaluate Performance. (a) Conference (b) Sponza Atrium (c) Sibenik Cathedral (d) Fairy Forest

A full chip consists of many TMs, each containing many TPs, sharing one or more on-chip L2 caches and off-chip memory and I/O bandwidth. Because of the parallel nature of ray-tracing, threads (and thus TPs) have no need to communicate with each other except to atomically divide the scene. Therefore, a full on-chip network is neither provided nor needed. In order to support multichip configurations, off-chip bandwidth is organized into lanes, which can be flexibly allocated between external memory and other I/O needs.

In TRaX, the lack of synchrony between ray threads reduces resource sharing conflicts between the cores and reduces the area and complexity of each core. With a shared multibanked Icache, the cores quickly reach a point where they are each accessing a different bank. Shared functional unit conflicts can be similarly reduced. Given the appropriate mix of shared resources and low-latency Dcache accesses, TRaX can sustain a high instruction issue rate without relying on latency hiding via thread context switching. This results in a different ratio of registers to functional resources for TRaX processing elements when compared to the hardware in commercial GPUs. The GPU approach involves sharing a number of thread states per core, only one of which can attempt to issue on each cycle. TRaX Thread Multiprocessors (TM) contain one thread state per Thread Processor (TP), each of which can potentially issue an instruction to a private per-core Functional Unit (FU) or one of the shared FUs. I believe this single thread-state approach is a more efficient use of register resources.

TRaX relies on asynchrony to sustain a high issue rate to the heavily shared resources, which enables simpler cores with reduced area, breaking the common wisdom that the SIMD approach is more area efficient than the MIMD model, at least for ray tracing. MIMD threads are allowed to progress through the program at their own pace, meaning that the Program Counters (PC) among a group of threads do not maintain the same value as is required for SIMD execution. Threads do not get significantly out of sync on the workload as a whole, thus maintaining coherent access to the scene data structure, and results in high cache hit rates.

#### 2.2.1 A Thread Processor

Each TP in a TRax TM can execute the single program based on its own program counter in a standard SPMD/MIMD fashion as defined in Chapter 1, where a software thread corresponds to a ray. In addition to the private program counter, each thread also maintains a private register file. The register file is a simple 2-read, 1-write static read only memory (SRAM) block. Register forwarding may be enabled in our simulator and allows operands to be available to instructions before the write-back stage of the pipeline. The type and number of independent functional units is variable in the TRaX simulator. More complex functional units are shared by the TPs in a TM. The TPs in a TM also share access to a multibanked instruction cache for the shared set of instructions. A block diagram of a thread processor can be found in Figure 2.2. Note that the local memory is optional and is not included in all TRaX designs, but it used in order to restrict the register file to 32. When the local memory is removed, the register file extends to 128 general purpose registers.

For a simple ray tracing application, large, complex instruction sets such as those seen in modern x86 processors are unnecessary. Our architecture implements a basic set of functional units with a simple but powerful instruction set architecture (ISA). We include bitwise instructions, branching, floating point/integer conversion, memory

Figure 2.2: Thread Processor Block Diagram

operations, floating point and integer add, subtract, multiply, reciprocal, and floating point compare. We also include reciprocal square root because that operation occurs with some frequency in graphics code for normalizing vectors.

Instructions are issued in order in each TP to reduce the complexity at the thread level. The execution is pipelined with the fetch and decode; each taking one cycle. The execution phase requires a variable number of cycles depending on the functional unit required, and the writeback takes a final cycle. Instructions issue in order, but may complete out of order. Thread processing stalls if needed data are not yet available for register forwarding, or if the desired functional unit is not available, but correct single-thread execution is guaranteed. Each TP is configured to issue a single instruction per cycle, although the simulator has support for higher thread issue width.

Because issue logic is split between the individual thread processor and the shared units in the TM, only some of the complexity in terms of dependence checking is internal to each thread. A simple table maintains instructions and their dependencies. Instructions enter the table in FIFO fashion, in program order, so that the oldest instruction is always the next available instruction. Issue logic checks only the status of this oldest instruction. Single thread performance is dependent on the programmer/compiler who must order instructions intelligently to hide functional unit latencies as often as possible. An important point to remember though, is that the overall system throughput is what is most important for ray tracing, not the performance of an individual thread.

Depending on which version of TRaX is being simulated, a number of thread features can be turned on or off as needed. The thread register file can be restricted to a size of 32 registers (the default in our compiler, though other register restrictions could be allowed) when using a compatible compiler, in which case a small local storage SRAM is used for thread-local stack space. However, when other compilation techniques are used, the architecture may instead be configured with a larger register file, allowing thread-local stack operations to be performed through special register offset instructions. The specifics of these configurations and their associated simulations are reported in Chapter 5.

## 2.2.2 A Collection of Threads in a Thread Multiprocessor

Each of the Thread Multiprocessors (TM) on a chip consists of a set of simple thread processors with shared L1 data cache and shared functional units, as shown in Figure 2.3(a). As mentioned above, the set of TPs in a TM share access to a many-banked instruction cache that can be varied in our simulations. Additionally, all threads in a TM share one multibanked L1 data cache of a modest size, also variable in our simulations. One example is 2K lines of 16-bytes each, direct mapped, with four banks. Many TMs on a multi-TM chip share a L2 unified data cache as the total code size is small enough to fit in a 4kB L1 instruction cache. Graphics processing is unique in that large blocks of memory are either read-only (e.g., scene data) or write-only (e.g., the frame buffer). To preserve the utility of the cache, write-once data are written around the cache. For our current ray tracing benchmarks no write data needs to be read back, so all writes are implemented to write around the cache (directly to the frame buffer). Separate cached and noncached write assembly instructions are provided to give the programmer control over which kind of write should occur. This significantly decreases thrashing in the cache by filtering out the largest source of pollution. Hence, cache hit rates are high and threads spend fewer cycles waiting on return data from the memory subsystem.

**Figure 2.3**: Potential TM and Multi-TM Chip Floor Plans. (a) TM Layout of 32 TPs and Shared Resources. (b) Chip with Multiple TMs Sharing L2 Caches.

Each shared functional unit is independently pipelined to complete execution in a given number of cycles, with the ability to issue a new instruction each cycle. In this way, each thread is potentially able to issue any instruction on any cycle. With the shared functional units, memory latencies and possible dependence issues, not all threads may be able to issue on every cycle. The issue unit gives threads priority to claim shared functional units in a round robin fashion. It is important to note that it is a good thing when the threads in a TM get a little out of sync with each other because it reduces the pressure on the shared functional units in any given cycle.

Each TP controls the execution of one ray-thread at a time. Because the parallelism we intend to exploit is at the thread level, and not at the instruction level inside a thread, many features commonly found in modern microprocessors, such as out-of-order execution, complex multilevel branch predictors, and speculation, are eliminated from our architecture. This allows available transistors, silicon area, and power to be devoted to parallelism. In general, complexity is sacrificed for expanded parallel execution. This will succeed in offering high-performance ray tracing if we can keep a large number of threads issuing on each cycle. Results in Chapter 5 show that with 32 TPs per TM, 50% of the threads can issue on average in every cycle for a variety of different scenes using an assembly-coded Whitted-style ray tracer [47] and a path tracer coded in a C-like language [46]. This metric can be considered roughly equivalent to the SIMD efficiency reported in similar studies using SIMD architectures with one important distinction. Often SIMD efficiency is inflated by allowing speculative execution to continue since the units would be in use anyway while that computation will end up being thrown away and not used in the generation of the final image.

#### 2.2.3 Top Level Chip